Liberty 是用来描述门级单元的时序、功耗、噪声和功能等行为的文本文件,贯穿于数字后端设计的各个阶段。

所有与时序分析相关的工具都可以使用本 Liberty Parser 解析 Liberty 文件。

EDA工具的核心基础设施

芯片设计龙头企业合作伙伴

亿方联创:基于底座串联国产全流程工具链,

为客户提供一站式芯片服务!

帮助您节省项目开发周期,让设计变得

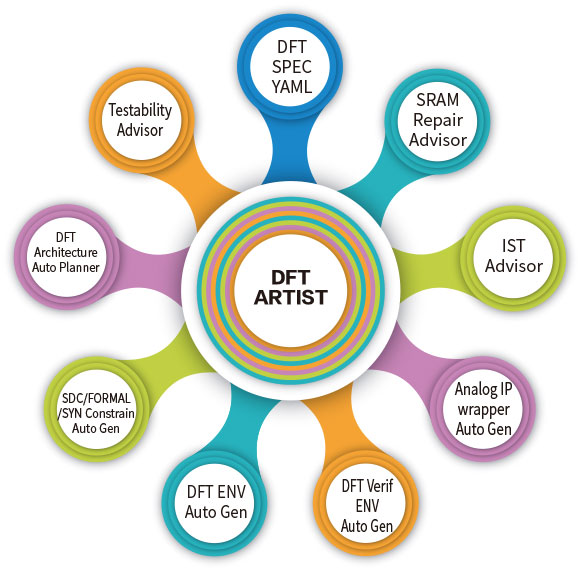

更加有趣,像做艺术品一样做DFT

DFT ARTIST

DFT ARTIST

APR ARTIST

APR ARTIST

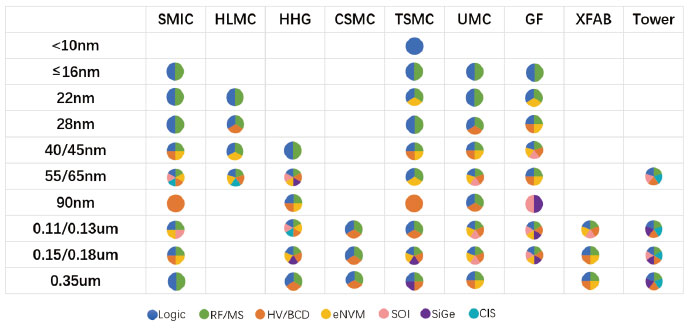

流片

流片